# Mikrocontrollertechnik

# MODUL

## Copyright ©

Das folgende Werk steht unter einer Creative Commons Lizenz (http://creativecommons.org). Der vollständige Text in Deutsch befindet sich auf http://creativecommons.org/licenses/by-nc-sa/2.0/de/legalcode.

#### **Creative Commons License Deed**

Namensnennung-NichtKommerziell-Weitergabe unter gleichen Bedingungen 2.0 Deutschland

#### Sie dürfen:

den Inhalt vervielfältigen, verbreiten und öffentlich aufführen

Bearbeitungen anfertigen

#### Zu den folgenden Bedingungen:

Namensnennung. Sie müssen den Namen des Autors/Rechtsinhabers nennen.

**Keine kommerzielle Nutzung**. Dieser Inhalt darf nicht für kommerzielle Zwecke verwendet werden.

Weitergabe unter gleichen Bedingungen. Wenn Sie diesen Inhalt bearbeiten oder in anderer Weise umgestalten, verändern oder als Grundlage für einen anderen Inhalt verwenden, dann dürfen Sie den neu entstandenen Inhalt nur unter Verwendung identischer Lizenzbedingungen weitergeben.

- Im Falle einer Verbreitung müssen Sie anderen die Lizenzbedingungen, unter die dieser Inhalt fällt, mitteilen.

- Jede dieser Bedingungen kann nach schriftlicher Einwilligung des Rechtsinhabers aufgehoben werden.

- Nothing in this license impairs or restricts the author's moral rights.

Die gesetzlichen Schranken des Urheberrechts bleiben hiervon unberührt.

Das Commons Deed ist eine Zusammenfassung des Lizenzvertrags in allgemeinverständlicher Sprache.

# **Inhaltsverzeichnis MODUL C**

| C0        | Wiederholung                                             | 1  |

|-----------|----------------------------------------------------------|----|

|           | Kurze Zusammenfassung Modul B                            | 1  |

| <b>C1</b> | Timer                                                    | 3  |

|           | Einführung                                               | 3  |

|           | Was ist ein Timer?                                       | 3  |

|           | Was kann man mit Timern tun?                             | 3  |

|           | Grundsätzliche Funktionsweise des Timers                 | ∠  |

|           | Der Timer als Zeitgeber                                  | 4  |

|           | Überlauf mit dem Timer 0                                 | 2  |

|           | Initialisierung des Timer 0 für den Überlauf-Interrupt   |    |

|           | Überlauf mit dem Timer 0 mit Voreinstellung              | 7  |

|           | Interrupt durch Vergleich mit dem Timer 0 (CTC)          | 8  |

|           | Vergleichsmodus (CTC) ohne Interrupt (Timer 0)           | 8  |

|           | Der Timer als Zähler (Counter)                           | g  |

|           | Timer 0 als Zähler (Counter)                             | g  |

|           | Pulsweitenmodulation mit dem Timer                       | 10 |

|           | Pulsweitenmodulation mit Timer 0                         | 10 |

|           | Funktionsweise des "Fast PWM"-Modus:                     | 11 |

|           | Initialisierung des Timer 0 für den "Fast-PWM"-Modus     | 12 |

|           | Die SF-Register des Timer 0                              | 13 |

|           | Das Timer/Counter Control Register TCCR0                 | 13 |

|           | Das Timer/Counter Interrupt Mask Register TIMSK          | 14 |

|           | Das Timer/Counter Interrupt Flag Register TIFR           | 14 |

|           | Das Timer/Counter Register 0 TCNT0                       |    |

|           | Das Output Compare Register 0 OCR0                       |    |

|           | Weitere Aufgaben                                         | 16 |

| C2        | Serielle Schnittstelle                                   | 17 |

|           | Hardware-Schnittstellen                                  | 17 |

|           | Bei Mikrocontrollern eingesetzte Hardware-Schnittstellen | 17 |

# Mikrocontrollertechnik

| Die Betriebsarten der Datenübertragung              | 18 |

|-----------------------------------------------------|----|

| Serielle Datenübertragung                           | 19 |

| Allgemeines                                         | 19 |

| Das synchrone Verfahren                             | 20 |

| Das asynchrone Verfahren                            | 21 |

| Das asynchrone und synchrone Verfahren im Vergleich | 21 |

| Größere Entfernungen                                | 21 |

| EIA-232                                             |    |

| Der Zeichenrahmen (SDU, Serial Data Unit)           | 23 |

| Die EIA-232-Schnittstellensignale                   | 25 |

| Die EIA-232-Verbindungen                            | 27 |

| Verbindung PC (DTE) – Modem (DCE)                   | 27 |

| Die Verbindung PC (DTE) – PC (DTE) (Nullmodemkabel) | 28 |

| Die Pegel der EIA-232-Schnittstellensignale         | 30 |

| Die Reichweite von EIA-232                          | 31 |

| Der Pegelwandlerbaustein 232                        | 31 |

| Die Datenflusskontrolle (bei EIA-232)               | 32 |

| Die Software-Flusskontrolle                         | 32 |

| Das XON/XOFF-Protokoll                              | 33 |

| Das ETX/ACK-Protokoll                               | 34 |

| Die Hardware-Flusskontrolle                         | 35 |

| Der USART des ATmega32A                             | 37 |

| Die Initialisierung der USART                       | 37 |

| Die USART Control und Status Register UCSRA         | 38 |

| Die USART Control und Status Register UCSRB         | 39 |

| Die USART Control und Status Register UCSRC         | 40 |

| Das USART Baud Rate (Doppel-) Register UBRR         | 41 |

| Das USART Daten Register UDR                        | 42 |

| Beispiel für eine Initialisierung                   | 43 |

| EIA-232-Sender und -Empfänger                       | 43 |

| Der USART als EIA-232-Sender (ohne Interrupt)       | 43 |

| Der USART als EIA-232-Empfänger (ohne Interrupt)    | 46 |

| Polling oder Interrupts?                            | 50 |

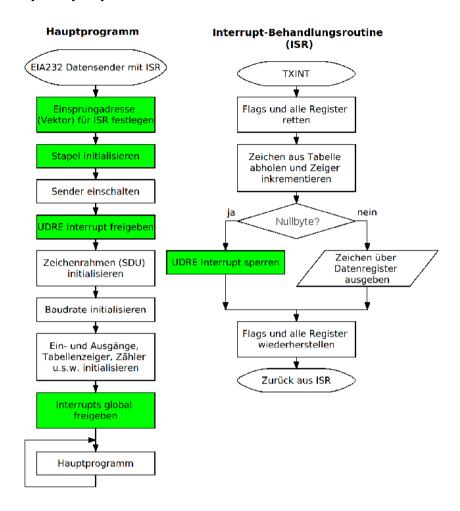

| USART-Sender mit Interrupts                         | 50 |

# Mikrocontrollertechnik

|    | USART-Empfänger mit Interrupts                                      | 53 |

|----|---------------------------------------------------------------------|----|

|    | Weitere Aufgaben                                                    | 54 |

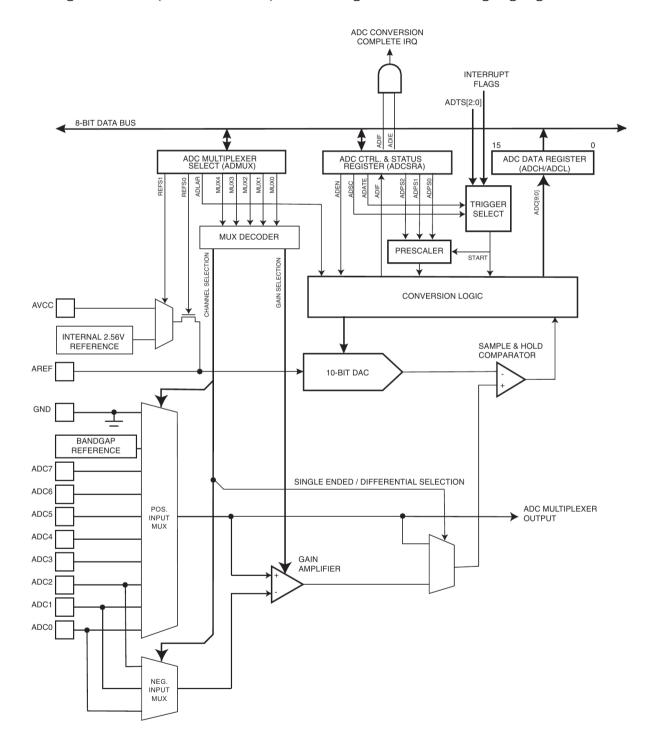

| C3 | A/D- und D/A-Wandler                                                | 59 |

|    | A/D-Wandler                                                         | 59 |

|    | Die Initialisierung des A/D-Wandlers                                | 61 |

|    | Die Referenzspannungsquelle (ADMUX)                                 | 61 |

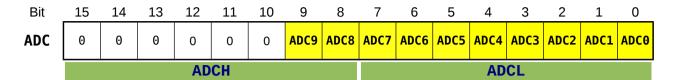

|    | Anordnung im Datenregister (ADMUX)                                  | 61 |

|    | Der Kanalmultiplexer (ADMUX)                                        | 62 |

|    | Der Vorteiler (ADCSRA)                                              | 63 |

|    | Weitere Einstellungen                                               | 63 |

|    | Polling                                                             | 64 |

|    | Interrupts                                                          | 64 |

|    | Beispiel für eine Initialisierung (Polling, Single Conversion Mode) | 65 |

|    | Die SF-Register des A/D-Wandlers                                    | 65 |

|    | Das ADMUX Register                                                  | 65 |

|    | Das ADC Kontroll- und Statusregister A                              | 67 |

|    | Das Sonderfunktionsregister SFIOR                                   | 68 |

|    | Das 16-Bit ADC Datenregister                                        | 69 |

|    | A/D-Wandlung mittels Polling                                        | 70 |

|    | Single Conversion Mode                                              | 70 |

|    | Free Running Mode                                                   | 71 |

|    | A/D-Wandlung mittels Interrupt (Auto Trigger)                       | 72 |

|    | Free Running Mode                                                   |    |

|    | Wandlung auslösen mit dem externen Interrupt 0                      |    |

|    | Wandlung auslösen mit dem Timer 0                                   |    |

|    | Weitere Aufgaben                                                    |    |

|    | D/A-Wandler                                                         | 78 |

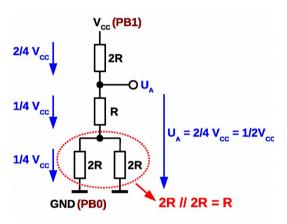

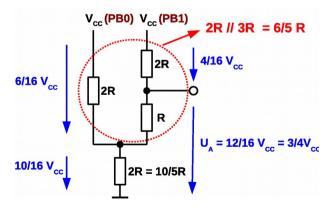

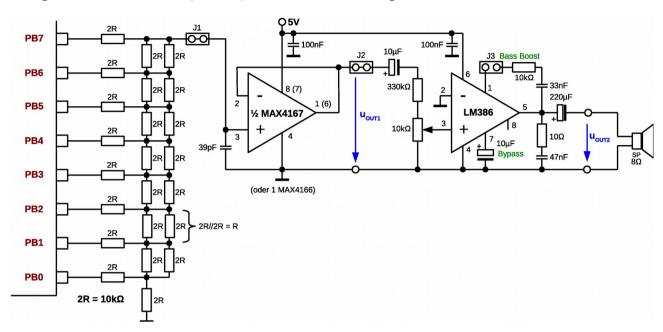

|    | Das R-2R-Netzwerk                                                   | 78 |

|    | Weitere Aufgaben                                                    | 81 |

| C4 | DDS                                                                 | 85 |

|    | Kurze Einführung                                                    | 85 |

|    | Warum DDS?                                                          | 85 |

|    | DDS mit dem Mikrocontroller                                         | 87 |

iv C0 Wiederholung

# **C0** Wiederholung

Die Grundlagen der Assembler-Programmierung aus dem Modul B sollen noch einmal kurz in Erinnerung gerufen werden.

# Kurze Zusammenfassung Modul B

- **Mechanische Schalter** an Eingängen ohne hardwaremäßige Entprellung müssen softwaremäßig mit Hilfe einer Zeitschleife **entprellt** werden (Pull-Up-Widerstände nicht vergessen; mit PIN und nicht mit PORT einlesen!).

- Bei der Benutzung von Unterprogrammen und Interrupt-Behandlungsroutinen (ISR) muss der **Stapel initialisiert** werden! Am Besten die 4 Zeilen zur Initialisierung im Template nie löschen.

- Auf die Arbeitsregister kann üblicherweise im gesamten Programm zugegriffen werden. Man spricht dann von **globalen Variablen**. Variablen die aber nur innerhalb eines Unterprogramms benötigt werden, sollten kein wertvolles Arbeitsregister blockieren. Innerhalb von Unterprogrammen und Interruptroutinen soll man mit **lokalen Variablen** arbeiten. Um Arbeitsregister für lokale Variablen zu befreien wird ihr Inhalt auf dem Stapel mit dem Befehl **push** zwischengespeichert. Vor dem Verlassen des Unterprogramms bzw. der Routine wird der Inhalt dann wieder ins Arbeitsregister zurückgespeichert (**pop**).

- Globale Variablen, die zur Übergabe von Daten an Unterprogramme dienen werden Parameter genannt. Am besten benutzt man immer die gleichen Arbeitsregister für die Parameterübergabe (in diesem Kurs das Doppelregister W (r24:r25 bzw. WL:WH)). Diese Arbeitsregister dürfen dann nicht auf den Stapel gerettet werden. Bei mehreren Parametern (z.B. Tabellen) sollte auf Speicherzellen im SRAM zurückgegriffen werden.

- Interrupts müssen einzeln für die lokale Baugruppe und global (**sei**) freigeschaltet werden. Zusätzlich muss der Interruptvektor mit einem Sprungbefehl zur ISR initialisiert werden.

- In einer Interruptroutine müssen zwingend alle Register die in der ISR verwendet werden, sowie auch das Statusregister **SREG**, auf dem Stapel gesichert (**push**) und von diesem wiederhergestellt (**pop**) werden. Die ISR schließt mit einem **reti** ab!

- Es existieren beim ATmega32A drei externe Interrupts (INT0, INT1, INT2) an PD2, PD3 und PB2. Im SF-Register MCUCR (bzw. MCUCSR für INT2) wird festgelegt, ob der Interrupt auf eine positive Flanke, eine negative Flanke oder eine beliebige Flanke bzw. einen Pegel (nur INT0 und INT1) reagiert. Erstaunlicherweise reicht es das MCUCR-Register (bzw. MCUCSR) zu initialisieren, damit die Interruptflags bei auftretender Flanke bereits gesetzt werden, sogar wenn der externe Interrupt noch gar nicht freigeschaltet ist!

- Wartet der Controller in einer Warteschleife auf ein Ereignis, so bezeichnet man das als Polling. Polling hat den Vorteil einer sequentiellen Programmierung, ist aber nicht sehr effektiv, da der Controller blockiert wird. Wenn möglich sollten deshalb Interrupts eingesetzt werden. Mit Interrupts ist Multitasking möglich, da einzelne Baugruppen unabhängig von Prozessor arbeiten können und beim Auftreten eines wichtigen Ereignisses dieses durch eine Unterbrechung mitteilen. Die Programmierung mittels Interrupts erhöht allerdings die Komplexität der Programme.

C0 Wiederholung 1

- △ C000

- Mit Hilfe der Interrupt-Eingänge INTO und INT1 soll ein Lauflicht beeinflusst werden. Die LEDs für das Lauflicht sind mit Port D verbunden.

Eine positive Flanke an INTO dreht die Richtung des Lauflichtes um, während an INT1 eine positive Flanke die Geschwindigkeit des Lauflichtes von schnell nach langsam oder umgedreht wechselt.

- a) Zeichne das Flussdiagramm zum Unterprogramm.

- b) Schreibe ein kommentiertes Assemblerprogramm.

Gib dem Programm den Namen "C000 INT driven running light.asm".

- c) Verbinde die beiden Interrupt-Eingänge miteinander und löse beide Interrupts *gleichzeitig* aus. Erkläre Deine Beobachtungen!

- △ **C001**

Ändere die vorige Aufgabe um, so dass man einen Schrittmotor ansteuern kann. INTO ist wieder für den Richtungswechsel und INT1 für eine Änderung der Geschwindigkeit verantwortlich.

Gib dem Programm den Namen "C001\_INT\_stepper motor.asm".

2 C0 Wiederholung

# C1 Timer

## **Einführung**

Die drei Timer des ATmega32 bieten sehr viele unterschiedliche Betriebsarten. Im folgenden Kapitel sollen nur einige der Betriebsarten kennen gelernt werden.

## Was ist ein Timer?

Ein Timerbaustein oder eine Timereinheit ist ein dualer Aufwärtszähler mit der Schrittweite Eins. Er ist zu jeder Zeit lese- und schreib-bar und kann vielfältig als Zeitgeber (*timer*) oder Zähler (*counter*) eingesetzt werden.

Als **Timer** wird der Systemtakt zum Zählen verwendet. Mittels Vorteiler kann dieser, falls nötig verringert werden.

Als **Counter** erhöhen externe Flanken am Timereingang (z.B. **T0**) den Zählstand.

Der Timer<sup>1</sup> ist eigenständig und läuft immer unabhängig vom Controllerkern und Programm. Nur mit ihr kann man zum Beispiel zeitliche Abstände präzise bestimmen oder mittels Interrupt in genauen Zeitabständen Ereignisse auslösen.

Im ATmega32 bzw. ATmega8 sind drei unabhängige Timereinheiten mit teils unterschiedlichen Eigenschaften verfügbar.

## Was kann man mit Timern tun?

Timer kann man einsetzen, um Zeitverzögerungen zu bewirken (anstatt von Zeitschleifen), als Frequenzgenerator oder -zähler (-messer), als Ereigniszähler für externe Signale, um Zeitabstände externer Signale zu messen, als Zeitgeber (Uhr), oder zur Pulsweitenmodulation zum Beispiel zum Ansteuern von Motoren,

Der ATmega32 enthält drei Universal-Timer mit folgenden Eigenschaften:

#### **Timer/Counter 0:** 8 Bit (0-255)

- Aufwärtszähler mit externem oder internem Takt mit Vorteiler (10 Bit)

- Überlauf-Interrupt (TOVO) und Vergleichswertinterrupt (OCFO)

- Frequenzgenerator

- Externer Ereigniszähler

- Pulsweitenmodulation PWM (fast PWM und phase correct PWM)

- Vergleichswertauswertung mit der Möglichkeit den Timer zurückzusetzen (*clear timer on compare match*, CTC-Modus)

#### **Timer/Counter 1:** 16 Bit (0-65535)

zusätzlich zu Timer 0:

- Zwei unabhängige Vergleichswertauswertungen

- 1 Der Einfachheit halber wird im Text nicht immer zwischen Timer und Counter unterschieden. Die Bezeichnung "Timer" wird allgemein für die Timereinheit verwendet.

- Input-Capture-Einheit (mit Rauschunterdrückung). Sie ermöglicht die Zeitmessung externer Signale (Stoppuhr)

- 4 Interruptquellen (Überlauf (T0V1), 2 mal Vergleichswert (OCF1A und OCF1B) und Input-Capture (ICF1))

#### **Timer/Counter 2:** 8 Bit (0-255)

ähnlich Timer 0, allerdings ohne externen Ereigniszähler! zusätzlich zu Timer 0:

• Timer 2 kann als Echtzeituhr (real time clock, RTC) verwendet werden.

## **Grundsätzliche Funktionsweise des Timers**

Ein Timer (Zeitgeber) oder Counter (Zähler) wird gesetzt (initialisiert) und gestartet. Danach läuft² (zählt) er unabhängig und unbeeinflusst vom Controllerkern und der anderen Peripherie bis man ihn stoppt. Hat der Timer seinen Höchstwert (255 bzw. 65535 für 8 und 16 Bit) erreicht, so beginnt er wieder bei null. Bei diesem Überlauf, oder bei einem anderen vorgegebenem Wert wird ein Flag gesetzt, das durch Polling abgefragt werden kann, oder es wird, was meist sinnvoller ist, ein Interrupt ausgelöst.

Man kann den Timer auch beim Erreichen eines Überlaufs oder eines Vergleichswertes ein Signal an einem Pin ausgeben lassen oder zum Beispiel die Zählrichtung umkehren.

Als Takt kann der AVR-Takt verwendet werden. Ein Vorteiler ermöglicht die Änderung der Taktfrequenz. Es kann aber auch ein externer Takt verwendet werden.

Zum Kennenlernen wird in den folgenden Kapiteln der 8-Bit Timer 0 verwendet. Alle Beispiele lassen sich auch auf die beiden anderen Timer übertragen, indem man die Bezeichnung der Register anpasst.

# Der Timer als Zeitgeber

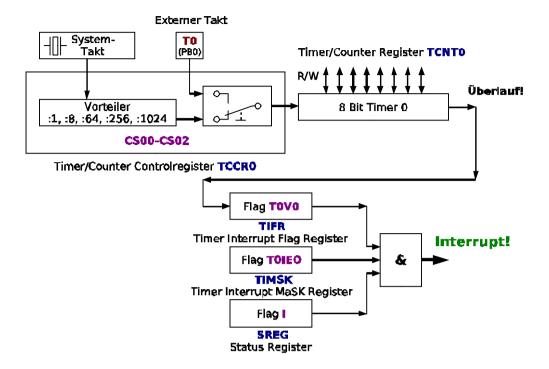

## Überlauf mit dem Timer 0

Nach der Aktivierung des Timers beginnt dieser gleich mit dem Zählen. Bei jedem Überlauf des Timers wird automatisch das Flag **T0V0** im SF-Register **TIFR** gesetzt. Bei Timer 0 also jedes Mal wenn dieser von 0 (Default-Startwert nach Reset) bis 255 gezählt hat (nach 256 Zählschritten).

Der Timer 0 soll nun bei jedem Überlauf periodisch einen Interrupt auslösen (Timer 0 Overflow Interrupt).

## Initialisierung des Timer 0 für den Überlauf-Interrupt

Zuerst muss geklärt werden mit welcher Taktrate gezählt werden soll. Diese Einstellung erfolgt mit den Bits 0 bis 2 (CS00-CS02) des Timer/Counter Controll Registers TCCR0. Folgende Tabelle bietet einen Überblick:

2 Der Timer wird automatisch inkrementiert oder dekrementiert.

| Bit 2 | Bit 1 | Bit 0 | Taktquelle                                                 |

|-------|-------|-------|------------------------------------------------------------|

| CS02  | CS01  | CS00  |                                                            |

| 0     | 0     | 0     | Timer Stopp (verbraucht keinen Strom)                      |

| 0     | 0     | 1     | Systemtakt (:1)                                            |

| 0     | 1     | 0     | Systemtakt / 8                                             |

| 0     | 1     | 1     | Systemtakt / 64                                            |

| 1     | 0     | 0     | Systemtakt / 256                                           |

| 1     | 0     | 1     | Systemtakt / 1024                                          |

| 1     | 1     | 0     | externer Takt: fallende Flanke an <b>T0</b> ( <b>PB0</b> ) |

| 1     | 1     | 1     | externer Takt: steigende Flanke an T0 (PB0)                |

**Bemerkung:** Durch Setzen der drei Bits **CS00-CS02** auf einen Wert größer als Null wird der Timerbaustein eingeschaltet. Er beginnt nach dieser Initialisierung gleich mit dem

Zählen ab Null, wenn kein Wert voreingestellt wurde.

Die Frequenz errechnet sich mit:

$$f = \frac{Systemtakt}{Vorteiler \cdot Z\ddot{a}hlschritte}$$

**Beispiel:** Als Vorteiler wurde 1024 gewählt bei einer Quarzfrequenz von 16 MHz. Damit

ergibt sich eine Zählfrequenz des Timers von 16 MHz / 1024 = 15625 Hz. Da jedes Interrupt nach 256 Zählschritten erfolgt, wird der Interrupt also mit einer

Frequenz von 15625 / 256 = 61,03515625 Hz aufgerufen.

**Hinweis:** Die obige Tabelle gilt ähnlich für Timer 1. Für Timer 2 ist sie allerdings nicht

gültig da dieser keine externen Signale verarbeiten kann. Dafür kann aber

zusätzlich ein Vorteiler von 32 und 128 eingestellt werden (siehe Datenblatt).

Damit das Interrupt ausgelöst wird müssen drei Bedingungen erfüllt sein:

- **1.** Das Flag **T0V0** im Timer Interrupt Flag Register **TIFR** muss Eins sein (**T0V0** = 1). Dies wird **automatisch gesetzt** wenn ein Überlauf erfolgt!

- **2.** Der **TO**-Interrupt muss erlaubt sein (**TOIE0** = 1 im Register **TIMSK**).

- **3.** Interrupts müssen global freigegeben sein (**I** in **SREG** = 1 mit "**sei**")

Um den Timer als Zeitgeber im Interrupt-Betrieb zu benutzen, müssen außer der üblichen Initialisierung also noch folgende Schritte erledigt werden:

• Sprungadresse für den Interrupt organisieren (aus der Definitionsdatei: **0VF0addr = 0x0016**) und der Interruptroutine einen Namen zuweisen (z. B. **INTT0**).

- Initialisierung des Stapels nicht vergessen!

- Die Timereinheit mit den Flags **CS00-CS02** im SF-Register **TCCR0** einschalten. Gleichzeitig wird der Vorteiler festgelegt. Da die oberen fünf Bit dieses Registers hier Null sind (normaler Modus, **OC0** normales Port Pin), muss hier nicht zwingend eine Maskierung eingesetzt werden:

```

;Timer einschalten und Vorteiler festlegen

ldi Tmp1,0x01 ;TCCR0 = 0b00000 001 (Systemtakt/1)

out TCCR0,Tmp1 ;

```

• **T0IE0** im SF-Register **TIMSK** mittels Maskierung setzen:

```

;Timer Interrupt erlauben

in Tmp1,TIMSK ;

ori Tmp1,0x01 ;Mit einer ODER-Maskierung (00000001b)

;Bit 0 (TOIE0) im TIMSK-Register auf eins setzen

out TIMSK,Tmp1 ;Timer 0-Overflow-Interrupt ein

```

• Interrupts global freigeben (sind bei Reset des Controllers per *default* gesperrt):

```

;Interrupts freigeben

sei ;Interrupts global freigeben (I-Bit im SREG)

```

Interruptroutine schreiben. Innerhalb der Routine müssen die Flags (SREG) und alle!,

innerhalb der Routine benutzten Register, auf den Stapel gerettet werden.

△ **C100** Es soll am Pin **PA0** mittels Timer 0-Interrupt ein Rechtecksignal durch Toggeln des Ausgangs erzeugt werden. Es wird ein Frequenzzähler oder Oszilloskop an das Pin angeschlossen. Um zu zeigen, dass die CPU (das Hauptprogramm) dadurch nicht belastet wird, soll das Hauptprogramm im Sekundentakt von null an aufwärts zählen und den Zählerstand am Sieben-Segment-Display ausgeben. Der Code für das Hauptprogramm ist vorgegeben (Unterprogrammbibliotheken für Display und Zeitschleifen müssen eingebunden werden):

- a) Errechne die zu erwartende Frequenz, wenn bei der Initialisierung des Timers der Vorteiler auf 256 eingestellt wird (Quarzfrequenz 16 MHz).

- b) Zeichne das Flussdiagramm und erstelle das Programm.

Nenne das Programm "C100 8bit timer0 ISR 0VF1.asm"

- c) Überprüfe die Frequenz mittels Zähler oder Oszilloskop.

## Überlauf mit dem Timer 0 mit Voreinstellung

Das Timerzählregister **TCNT0** kann nicht nur ausgelesen werden, sondern auch beschrieben werden. Dies ermöglicht es die Zählschritte bis zum Überlauf zu verringern. Wird das Register zum Beispiel mit dem Startwert 200 voreingestellt, so zählt der Timer von 200 bis 255, also nur 56 Schritte.

Soll jetzt, um zum Beispiel eine höhere Frequenz zu erzeugen, der Timer nach jedem Überlauf mit einem festen Startwert versehen werden, so muss das gleich am Anfang der Interruptroutine (vor den Push-Befehlen!) geschehen um die Genauigkeit des Timers nicht zu gefährden. Am einfachsten wird der Startwert in einer globalen Variablen bei der Initialisierung festgelegt.

△ **C101** Ändere das Programm **C100** so um, dass der Timer 0 immer mit dem Startwert 150 beginnt.

Nenne das neue Programm "C101 8bit timer0 ISR OVF2.asm".

- a) Ermittle rechnerisch und per Zähler (Oszilloskop) die erzeugte Frequenz.

- b) Errechne den Startwert, der benötigt wird um eine Frequenz von 440 Hz (Kammereton A (LA)) zu erzeugen. Überprüfe das Ergebnis.

△ **C102** Ändere das Programm **C101** so um, dass im Hauptprogramm im Sekundenrythmus der Startwert des Timers ab Null jeweils um 5 erhöht wird. Nenne das neue Programm "**C102** 8bit timer0 ISR 0VF3.asm".

## Interrupt durch Vergleich mit dem Timer 0 (CTC)

Neben dem Zählregister existiert ein Vergleichregister **OCR0**, das eine einfachere Einstellung der Zählschritte erlaubt. Statt des Überlauf-Interrupts wird der Vergleich-Interrupt im **TIMSK** Register eingeschaltet und natürlich auch die entsprechende Sprungadresse initialisiert (.**ORG OCR0addr**).

Im **TCCR0**-Register wird wie gehabt der Teiler festgelegt. Es wird der **CTC-Modus** (*clear timer on compare match*) eingeschaltet mit den beiden *Waveform Generation Mode* Bits **WGM0=10**. Die beiden *Compare Match Output Mode* Bits bleiben auf null **COM0=00**. **OCO (PB3)** bleibt abgeschaltet (normales Port-Pin; siehe weiter unten).

Im Programm wird das Vergleichsregister mit den Zählschritten initialisiert um eine bestimmte Frequenz der Interruptroutine zu erhalten.

△ **C103** Programmiere den Timer 0 im Interrupt-CTC-Modus, so dass eine Frequenz von 440 Hz (Kammereton A (LA)) am Pin PC7 erzeugt wird. Überprüfe das Ergebnis. Nenne das neue Programm "C103\_8bit\_timer0\_ISR\_CTC.asm".

## Vergleichsmodus (CTC) ohne Interrupt (Timer 0)

Der Timer 0 hat auch eine Funktion um Frequenzen ohne Interrupt zu erzeugen (Frequenzgenerator)! Ein fest zugeordnetes Pin OCO (PB3) wird bei entsprechender Initialisierung getoggelt, sobald ein im Output Compare Register OCRO eingetragener Wert erreicht wurde (siehe auch PWM).

Dies beiden Compare Match Output Mode Bit im TCCR0-SF-Register entscheiden über den Zustand des Ausgangspin.

| COM01 COM00<br>2 <sup>1</sup> 2 <sup>0</sup> | Verhalten im normalen Modus:              |

|----------------------------------------------|-------------------------------------------|

| 00                                           | 0C0 abgeschaltet (normales Port-Pin)      |

| 01                                           | Toggele 0C0 bei Vergleichsübereinstimmung |

| 10                                           | Lösche OCO bei Vergleichsübereinstimmung  |

| 11                                           | Setze 0C0 bei Vergleichsübereinstimmung   |

C104 Programmiere den Timer 0 im CTC-Modus ohne Interrupt, so dass er folgendes Lied abspielt. Der zweite Wert in der Tabelle entspricht der Pausendauer (1 = 200ms, 2 = 100ms, 4 = 50ms usw.). Zum Schluss jeder Note wird eine kurze Pause (100μs) eingelegt. 0xFF bedeutet, dass das Lied vorbei ist.

Nenne das neue Programm "C104 8bit timer0 CTC.asm".

; Zaehlschritte fuer Timer0 (CTC) mit Vorteiler 64 .EQU Si2 = 254

```

. EOU

Do3

= 239

.EOU

Do3d

= 226

. EQU

Re3

= 213

. EQU

Re3d = 201

. EQU

Mi3

= 190

. EQU

Fa3

= 179

= 169

EQU

Fa3d

= 160

. EQU

So13

EQU

Sol3d = 151

. EQU

La3

= 143

= 135

La3d

EQU

. EQU

Si3

= 127

EQU

Do4

= 120

Do4d = 113

. EQU

. EQU

Re4

= 107

= 101

.EQU

Re4d

. EQU

Mi4

= 95

EQU

Fa4

= 90

. EQU

Fa4d

= 58

EQU

Sol4

= 80

.EQU

Sol4d = 76

EQU

La4

= 72

EQU

La4d

= 68

EQU

Si4

= 64

Do5

. EQU

= 60

EQU

Do5d

= 57

Re5

. EQU

= 54

EQU

Re5d

= 51

Mi5

= 48

. EQU

EQU

Fa5

= 43

EQU

Fa5d

EQU

Sol5

= 40

Sol5d = 38

. EQU

. EQU

La5

= 36

. EQU

La5d = 34

Zeitdauer 1 = ganze Note, 2 = halbe Note, 4 = Viertelnote etc

NOTET1: .DB

Fa3, 4, Sol3d, 6, Fa3, 8, Fa3, 16, La3d, 8, Fa3, 8, Re3d, 8

.DB

Fa3, 4, Do4, 6, Fa3, 8, Fa3, 16, Do4d, 8, Do4, 8, Sol3d, 8

.DB

Fa3, 8, Do4, 8, Fa4, 8, Fa3, 16, Re3d, 8, Re3d, 16, Do3, 8, Sol3, 8, Fa3, 8

.DB

Fa3, 2, 0, 2

. DB

Fa3, 4, Sol3d, 6, Fa3, 8, Fa3, 16, La3d, 8, Fa3, 8, Re3d, 8

.DB

Fa3, 4, Do4, 6, Fa3, 8, Fa3, 16, Do4d, 8, Do4, 8, Sol3d, 8

. DB

Fa3, 8, Do4, 8, Fa4, 8, Fa3, 16, Re3d, 8, Re3d, 16, Do3, 8, Sol3, 8, Fa3, 8

.DB

Fa3, 2, 0, 2

.DB

0xFF,0xFF

```

# Der Timer als Zähler (Counter)

Über ein reserviertes Pin kann die fallende oder die steigende Flanke eines externen Signals dazu verwendet werden den Zähler zu erhöhen. So ist es möglich den Timer als Zähler externer Ereignisse einzusetzen.

## Timer 0 als Zähler (Counter)

Um den Timer als Zähler einzusetzen, reicht es, über die Bits **CS00-CS02** im Timer/Counter Control Register **TCCR0** statt einem internen Takt einen externen Takt auszuwählen. Dabei kann die steigende Flanke oder die fallende Flanke des externen Signals zum Zählen genutzt werden. Es ist sinnvoll, da meist mit Pull-Up Widerständen gearbeitet wird (negative Logik), die fallende Flanke zum Zählen zu verwenden. Das externe Signal muss an Pin **T0** (**PB0**) angelegt werden.

△ C105

Ein nicht entprellter Taster soll als Signalquelle für den Zähler dienen (**T0** als Eingang initialisieren und Pull-Up einschalten!). Der Zählstand (**TCNT0**) soll im Hauptprogramm im Sekundentakt angezeigt werden. Der Zähler ist auf den Wert 246 voreingestellt, und beim Überlauf soll eine LED (**PA0**) umgeschaltet werden. Nenne das neue Programm "**C105 8bit counter0 1.asm**".

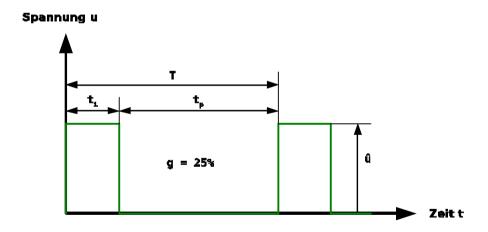

## Pulsweitenmodulation mit dem Timer

Die Leistung kann bei vielen elektrischen Geräten durch Veränderung der Spannung gesteuert werden. Es gibt aber auch Geräte wo dies nicht zufriedenstellend funktioniert, da diese Geräte zum Beispiel eine Mindestspannung zum Arbeiten benötigen (LED, Motor). Die Pulsweitenmodulation bietet hier Abhilfe und lässt sich (anders als eine variable Spannung) sehr leicht mit einem Mikrocontroller realisieren.

Bei der Pulsweitenmodulation wird eine Rechteckspannung mit fester Frequenz verwendet, bei der der Tastgrad<sup>3</sup> (*duty cycle*) verändert wird. Die Impulsweite im Verhältnis zur Periodendauer wird meist in Prozent ausgedrückt.

$$\label{eq:mpulsdauer} \begin{array}{ll} Impulsdauer \ t_i & Pausendauer \ t_p \\ \\ Tastgrad \ g = \frac{t_i}{T} & Periodendauer \ T = t_i + t_p \end{array}$$

## Pulsweitenmodulation mit Timer 0

Die Pulsweitenmodulation lässt mit dem Timer relativ einfach softwaremäßig realisieren. Bei dieser Variante mit Überlauf- und Vergleichswert-Interrupt kann dann jedes beliebige Ausgangspin genutzt werden.

3 Oft findet man auch den Begriff "Tastverhältnis". Dieser Begriff ist allerdings nicht einheitlich definiert. Oft findet man ihn als Kehrwert des Tastgrads, manchmal ist er gleich wie der Tastgrad definiert, oder auch als Verhältnis zwischen Impuls- und Pausendauer.

Noch einfacher geht es allerdings, wenn der Timer alle Aufgaben selber übernimmt. Dieser von ATMEL® genannte "Fast PWM"-Modus benötigt keine Interruptroutinen und schont somit die Ressourcen des Controllers. Als Ausgang muss für Timer 0 der **OCO**-Pin (**PB3**) genutzt werden.

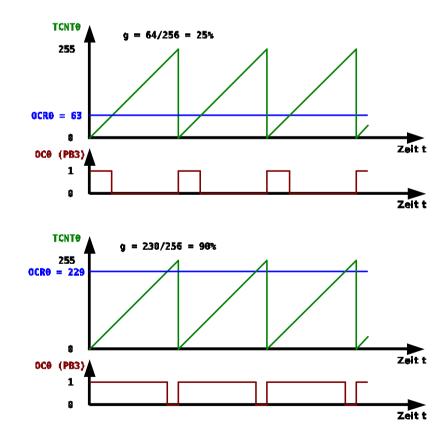

## Funktionsweise des "Fast PWM"-Modus:

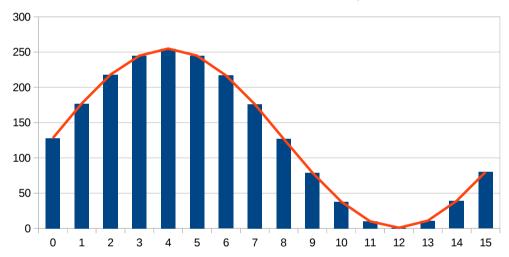

Der Timer 0 zählt durchgehend von 0 bis 255 und beginnt dann wieder bei 0 (Zählregister **TCNT0**). Ein gesamter Durchlauf entspricht der Periodendauer des PWM-Signals. Die Frequenz wurde durch den Systemtakt und den Vorteiler bestimmt.

$$f = \frac{Systemtakt}{Vorteiler \cdot 256}$$

Am Ausgangspin **OCO** liegt High-Pegel an (nicht-invertierender Modus).

In einem zweiten Register, dem sogenannten Vergleichsregister **OCRO**, wird ein Vergleichswert festgelegt. Erreicht der Zählwert diesen Vergleichswert, so kippt der Pegel am Ausgangspin **OCO** auf Low-Pegel. Der Zähler zählt ungerührt weiter, um beim Überlauf das Ausgangspin wieder auf High-Pegel zu setzen. Der Vergleichswert bestimmt den Tastgrad!

## Initialisierung des Timer 0 für den "Fast-PWM"-Modus

Um den "Fast PWM"-Modus einzuschalten müssen die Bits **WGM00** und **WGM01** im Kontrollregister **TCCR0** beide auf Eins gesetzt werden. In diesem Modus wird mit **COM01** = 1 und **COM00** = 0 (beide ebenfalls im Kontrollregister **TCCR0**) der nicht invertierende PWM-Modus ausgewählt (invertierender Modus: Modus: **COM01** = 1 und **COM00** = 1). Über die Bits **CS00-CS02** wird über den Vorteiler die Frequenz eingestellt. Das letzte freie Bit (**FOC0**) im Register **TCCR0** muss in diesem Modus auf null gesetzt werden.

Zusätzlich zur Initialisierung des Kontrollregisters **TCCR0** muss nur noch das Pin **OC0** (**PB3**) als Ausgang initialisiert werden und ein Vergleichswert muss ins Vergleichsregister **OCR0** Register geschrieben werden.

Die ganze Initialisierung besteht zum Beispiel aus folgenden Zeilen:

- △ **C106** Die Helligkeit einer LED soll im Sekundenrhythmus erhöht werden. Dazu soll im Hauptprogramm einmal pro Sekunde der Vergleichswert ab 0 um 5 erhöht werden. Die Siebensegmentanzeige gibt gleichzeitig den Vergleichswert aus.

- a) Schreibe das Programm und nenne es "C106 8bit timer0 pwm 1.asm".

- b) Betrachte die Spannung mit einem Oszilloskop. Interessant ist auch die Ausgabe mittels Summer.

- c) Welchen Einfluss hat die Frequenz?

- $^{\circ}$  C107 Mit Hilfe einer PWM soll ein Funktionsgenerator (Rechteck, Sinus, Dreieck und Sägezahn) mit einer festen Frequenz von 440 Hz programmiert werden. Die PWM arbeitet mit der höchsten Frequenz (Vorteiler = 1). Ein Tiefpass am Ausgang (C = 47 nF, R = 1,2 kΩ) siebt den hochfrequenten Teil der PWM aus. Die Wellenformen sollen sich in Tabellen (8 Bit, 256 Werte) befinden(siehe Kapitel DA Wandler).

- a) Berechne die Grenzfrequenz des Tiefpasses.

- b) Schreibe das Programm und nenne es "C107 PWM wavegen.asm".

- c) Betrachte die Spannung mit einem Oszilloskop. Interessant ist auch die Ausgabe mittels Summer.

**Bemerkung:** Im normalen Modus kann mit Hilfe des Vergleichswertregisters ein zusätzlicher Interrupt bei Übereinstimmung des Zählwertes mit dem Vergleichswert ausgelöst werden (*Output Compare Match Interrupt*). Im sogenannten CTC-Modus (*Clear Timer on Compare Match Mode*) kann der Timer bei Erreichen des Vergleichswertes auch zurückgesetzt werden.

# Die SF-Register des Timer 0

## **Das Timer/Counter Control Register TCCR0**

Das **Timer/Counter Control Register 0** befindet sich auf der SRAM-Adresse **0x0053** (SF-Register-Adresse **0x33**) und wird mit der Abkürzung "**TCCR0**" angesprochen (Definitionsdatei). Die Befehle **sbi**, **cbi**, **sbic** und **sbis** können nicht verwendet werden.

#### TCCR0 = Timer/Counter Control Register 0

| Bit           | 7    | 6     | 5     | 4     | 3     | 2    | 1    | 0    |

|---------------|------|-------|-------|-------|-------|------|------|------|

| TCCR0<br>0x33 | F0C0 | WGM00 | COM01 | COMOO | WGM01 | CS02 | CS01 | CS00 |

| Startwert     | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    |

| Read/Write    | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  |

#### WGMOn Waveform Generation Mode

WGM01, WGM00

Mit diesen zwei Bit wird der Operationsmodus des Timer festgelegt:

| WGM01 WGM00<br>2 <sup>1</sup> 2 <sup>0</sup> | Modus:                                   |

|----------------------------------------------|------------------------------------------|

| 00                                           | Normaler Modus                           |

| 01                                           | Phasenkorrekter PWM-Modus                |

| 10                                           | CTC-Modus (clear timer on compare match) |

| 11                                           | Fast PWM-Modus                           |

#### COMen

#### Compare Match Output Mode COM01, COM00

Mit diesen zwei Bit wird das Verhalten des Ausgangspin **OCO** festgelegt. Je nach Modus ändert das Verhalten:

| COM01 COM00<br>2 <sup>1</sup> 2 <sup>0</sup> | Verhalten im normalen Modus:              |

|----------------------------------------------|-------------------------------------------|

| 00                                           | 0C0 abgeschaltet (normales Port-Pin)      |

| 01                                           | Toggele 0C0 bei Vergleichsübereinstimmung |

| 10                                           | Lösche 0C0 bei Vergleichsübereinstimmung  |

| 11                                           | Setze OCO bei Vergleichsübereinstimmung   |

| COM01 COM00<br>2 <sup>1</sup> 2 <sup>0</sup> | Verhalten im Fast-PWM Modus:              |

| 00                                           | 0C0 abgeschaltet (normales Port-Pin)      |

| 01                                           | Reserviert                                |

| 10                                           | nicht-invertierender Fast-PWM-Modus       |

| 11                                           | invertierender Fast-PWM-Modus             |

#### CS<sub>0</sub>n

#### Clock Select Timer 0

CS02, CS01, CS00

Mit diesen drei Bit wird die Taktquelle für Timer 0 festgelegt.

| CS02 CS01 CS00<br>2 <sup>2</sup> 2 <sup>1</sup> 2 <sup>0</sup> | Taktquelle:                                    |

|----------------------------------------------------------------|------------------------------------------------|

| 000                                                            | Timer Stopp                                    |

|                                                                | (verbraucht keinen Strom, default nach RESET!) |

| 001                                                            | Systemtakt (:1)                                |

| 010 | Systemtakt / 8                              |

|-----|---------------------------------------------|

| 011 | Systemtakt / 64                             |

| 100 | Systemtakt / 256                            |

| 101 | Systemtakt / 1024                           |

| 110 | externer Takt: fallende Flanke an T0 (PB0)  |

| 111 | externer Takt: steigende Flanke an T0 (PB0) |

Weitere Informationen findet man im Datenblatt.

## **Das Timer/Counter Interrupt Mask Register TIMSK**

Das **Timer/Counter Interrupt Mask Register** befindet sich auf der SRAM-Adresse **0x0059** (SF-Register-Adresse **0x39**) und wird mit der Abkürzung "**TIMSK**" angesprochen (Definitionsdatei). Die Befehle **sbi**, **cbi**, **sbic** und **sbis** können nicht verwendet werden.

#### TIMSK = Timer/Counter Interrupt Mask Register

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|

| TIMSK<br>0x39 | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 |

| Startwert     | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   |

#### **OCIE0** Timer/Counter 0 Output Compare Match Interrupt Enable

- **0** kein **0CF0**-Interrupt erlaubt.

- Das Setzen dieses Bit **ermöglicht das Auslösen eines Interrupts** in dem Moment, wo das **OCFO**-Flag (**TIFR**) gesetzt wird, also eine Übereinstimmung zwischen dem Zählregister **TCNTO** und dem Vergleichsregister **OCRO** stattgefunden hat, oder wenn das Flag manuell gesetzt wurde. Interrupts müssen dazu global frei gegeben sein (**I**=1 im **SREG** mit "**Sei**").

#### **TOIE0** Timer/Counter 0 Overflow Interrupt Enable

- **0** kein **TOVO**-Interrupt erlaubt.

- Das Setzen dieses Bit **ermöglicht das Auslösen eines Interrupts** in dem Moment, wo das **TOVO**-Flag (**TIFR**) gesetzt wird, also ein Überlauf auftrat oder wenn das Flag manuell gesetzt wurde. Interrupts müssen dazu global frei gegeben sein (**I**=1 im **SREG** mit "**sei**").

## Das Timer/Counter Interrupt Flag Register TIFR

Das **Timer/Counter Interrupt Flag Register** befindet sich auf der SRAM-Adresse **0x0058** (SF-Register-Adresse **0x38**) und wird mit der Abkürzung "**TIFR**" angesprochen (Definitionsdatei). Die Befehle **sbi. cbi. sbic** und **sbis** können nicht verwendet werden.

#### TIFR = Timer/Counter Interrupt Flag Register

| Bit          | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    |

|--------------|------|------|------|-------|-------|------|------|------|

| TIFR<br>0x38 | 0CF2 | T0V2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 |

| Startwert    | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |

| Read/Write   | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  |

#### **OCFO** Output Compare Flag 0

- 6 Keine Übereinstimmung des Inhalts des Zählregister mit dem Inhalt des Vergleichsregisters.

- Bei Übereinstimmung (*compare match*) des Wertes im Zählregister **TCNT0** mit dem Wert im Vergleichsregister **OCR0** wird das Flag gesetzt. Das Flag wird automatisch gelöscht, wenn der **OC**-Interrupt ausgeführt wird. Manuell kann das Flag durch das **Schreiben einer Eins!** gelöscht werden.

#### **TOV0** Timer/Counter 0 Overflow Flag

- **0** Keine Überlauf eingetreten.

- Tritt ein Überlauf des Zählregisters **TCNT0** auf so wird das Flag gesetzt. Das Flag wird automatisch gelöscht, wenn der **OV**-Interrupt ausgeführt wird. Manuell kann das Flag durch das **Schreiben einer Eins!** gelöscht werden.

## Das Timer/Counter Register 0 TCNT0

Das **Timer/Counter Register 0** befindet sich auf der SRAM-Adresse **0x0052** (SF-Register-Adresse **0x32**) und wird mit der Abkürzung "**TCNT0**" angesprochen (Definitionsdatei). Die Befehle **sbi**, **cbi**, **sbic** und **sbis** können nicht verwendet werden. Das Register ist les- und schreibbar.

#### TCNT0 = Timer/Counter Register 0

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| TCNT0<br>0x32 | TCNT07 | TCNT06 | TCNT05 | TCNT04 | TCNT03 | TCNT02 | TCNT01 | TCNT00 |

| Startwert     | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | R/W    |

## **Das Output Compare Register 0 OCR0**

Das **Output Compare Register 0** befindet sich auf der SRAM-Adresse **0x005C** (SF-Register-Adresse **0x3C**) und wird mit der Abkürzung "**OCR0**" angesprochen (Definitionsdatei). Die Befehle **sbi**, **cbi**, **sbic** und **sbis** können nicht verwendet werden. Das Register ist les- und schreibbar.

#### OCR0 = Output Compare Register 0

| Bit          | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| OCRO<br>0x3C | 0CR07 | OCR06 | 0CR05 | OCR04 | 0CR03 | 0CR02 | 0CR01 | OCR00 |

| Startwert    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Read/Write   | R/W   |

## Weitere Aufgaben

△ **C108** Ändere das erste Programm dieses Kapitels so um, dass es mit dem 16-Bit-Timer 1 arbeitet. Es soll die gleiche Frequenz erzeugt werden! Ermittle die für Timer 1 benötigten Register (Datenblatt).

Nenne das neue Programm "C108\_16bit\_timer1\_1.asm".

(Achtung!! Wenn mit 16 Bit (SF Doppelregister) gearbeitet wird, soll bei beiden **in** oder **out** Befehlen **cli** vor und sei hinten angestellt werden damit Interrupts das Lesen nicht beeinflussen können!!)

# **C2** Serielle Schnittstelle

## Hardware-Schnittstellen

Die Schnittstelle oder Interface ist ein Teil des Computers und dient der Kommunikation (Datenaustausch) mit peripheren Geräten.

Periphere Geräte müssen dabei nicht extern sein (Beispiel: SATA-Festplatte im PC). Eine Schnittstelle erkennt man oft am Steckersystem, mit welchem das periphere Gerät angeschlossen wird. Neben Anpassungsschaltkreisen und der Steckervorrichtung ist für eine Hardware-Schnittstelle meist auch ein steuernder Prozessor (inkl. Software) nötig.

Industrienormen definieren standardisierte Schnittstellen und ermöglichen so, dass Komponenten verschiedener Hersteller miteinander kommunizieren und gegeneinander ausgetauscht werden können. Die Komponenten sind dann zueinander kompatibel.

Unterscheiden kann man Hardware-Schnittstellen nach folgenden Kriterien:

- Digital Analog

- Seriell Parallel

- Synchron Asynchron

- Mechanische Eigenschaften

**Bemerkung:** Durch Veränderungen und Verbesserungen in der Datenverarbeitung sind viele neue Schnittstellen digital, seriell und synchron.

## Beispiele von digitalen Hardware-Schnittstellen:

• **Parallel:** PCI, AGP, SCSI, ATA/ATAPI, IEC-625, HP-IB, IEEE-488, IEEE 1284 (früher Centronics)

• Seriell: USB, Firewire, EIA-232 (früher RS-232 oder V24), EIA-485

(früher RS-485), I2C, SPI, S-ATA, PCI-Express, HDMI, IrDA, Bluetooth, MIDI, S/P-DIF, CAN-Bus, S0-Bus (ISDN), Ethernet,

WLAN.

## Bei Mikrocontrollern eingesetzte Hardware-Schnittstellen

Die klassische serielle asynchrone Schnittstelle wird wegen ihrer Einfachheit auch heute noch gerne bei Mikrocontrollern eingesetzt. Die meisten Mikrocontroller besitzen einen internen Baustein (UART oder USART; siehe später) für diese Schnittstelle.

I<sub>2</sub>C

Die von Philipps entwickelte synchrone Master-Slave Schnittstelle, (*Inter-Integrated Circuit*; gesprochen I-Quadrat-C) zur Kommunikation zwischen ICs, benötigt nur drei Leitungen (Halbduplex) und ist in der Unterhaltungselektronik weit verbreitet (viele ansteuerbare Spezial-ICs). Die Taktrate und die überbrückbare Distanz sind recht gering. Bei einigen AVR-Controllern wird die Schnittstelle hardwaremäßig unterstützt und heißt TWI-Schnittstelle (*Two Wire Bus*).

SPI

SPI (*Serial Periphal Interface*) ist ein Bus-System (Master-Slave, 5 Leitungen), das von Motorola für die Kommunikation zwischen Mikrocontrollern entwickelt wurde (keine großen Distanzen). Es arbeitet synchron in Vollduplex mit hoher Taktgeschwindigkeit (bis zu mehreren 10 MHz). Die SPI-Schnittstelle wird bei der AVR-Familie zur *In-System-*Programmierung genutzt und hardwaremäßig unterstützt.

**USB**

Die USB-Schnittstelle verdrängt immer mehr die serielle Schnittstelle bei den PCs. Möchte man den Controller an der USB-Schnittstelle betreiben, so ist dies mit entsprechenden USB-EIA-232 Wandlerbausteinen (z. B. FT232BM) möglich, oder mit USB-EIA-232-Adapter-Verbindungskabeln. Auch existieren Mikrocontroller mit integrierter USB-Schnittstelle (z. B. ATmega32U4). Es ist sogar gelungen die komplexe USB-Schnittstelle in ihrer Version 1.1 softwaremäßig auf einem ATmega8A zu implementieren.

**Ethernet**

Auch für die Ethernet-Schnittstelle gibt es Wandlerbausteine nach EIA-232 (z. B. Lantronix X-Port), die allerdings noch recht teuer sind. Softwaremäßige Lösungen (Webserver mit ATmega32A und Ethernetchip (z. B. ENC28J60)) existieren ebenso.

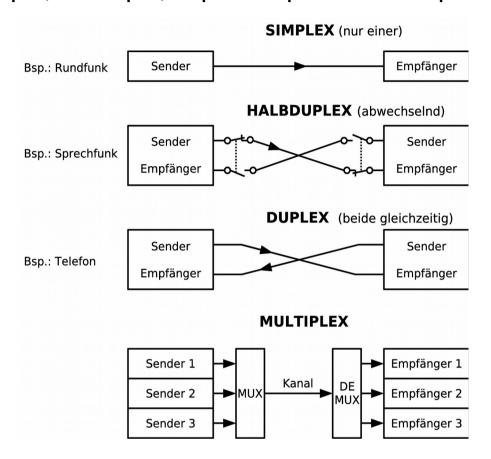

# Die Betriebsarten der Datenübertragung

Man kann bei der Datenübertragung folgende Betriebsarten unterscheiden:

- **Seriell Parallel** (siehe nächstes Kapitel)

- **Synchron Asynchron** (siehe nächstes Kapitel)

- Simplex Halbduplex Vollduplex Multiplex

Beim **Simplexbetrieb** (Richtungsbetrieb) erfolgt die Übertragung nur in eine Richtung. Es kann kein Feedback (z. B. Fehlermitteilung) erfolgen. Der Simplexbetrieb wird in der Verteilerkommunikation (z. B. Rundfunk) verwendet.

Der **Halbduplexbetrieb** (Semiduplex, Wechselbetrieb) erfolgt die Übertragung zeitlich abwechselnd. Beide Partner benötigen Sende- und Empfangseinrichtungen, die aber nicht gleichzeitig betreibbar sein müssen. Auch die Übertragungsstrecke muss nicht unbedingt doppelt ausgeführt sein (Beispiel Sprechfunk).

Beim **Vollduplexbetrieb** (Duplex, Gegenbetrieb) findet die Kommunikation gleichzeitig in beide Richtungen statt. Auch die Strecke muss Vollduplex zulassen und ist meist doppelt ausgeführt. Neue Techniken wie die Echokompensation (ISDN) erlauben allerdings auch Vollduplex auf nur einer Leitung.

Eine Sonderform der drei Betriebsarten ist der **Multiplexbetrieb** (MUX, MPX). Die Anzahl von Übertragungskanälen ist nicht beliebig erweiterbar. Eine bessere Ausnutzung der Kanalkapazität ermöglicht die gleichzeitige mehrfache Nutzung eines Kanals mit Hilfe von Multiplexern (Schaltung zum Multiplexen) und Demultiplexern. Man unterscheidet als Verfahren: **Raummultiplex**, **Zeitmultiplex**, **Frequenzmultiplex** und **Codemultiplex**.

# Serielle Datenübertragung

## **Allgemeines**

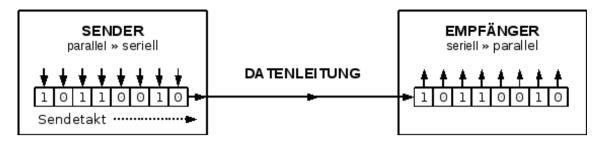

Bei der seriellen Datenübertragung wird der Datenaustausch zwischen Datensender und Datenempfänger **bitweise nacheinander** über nur eine Leitung vollzogen. Da die Daten oft in paralleler Form vorliegen, muss der Sender über ein Schieberegister eine **parallel-seriell Wandlung** realisieren. Die Taktung übernimmt meist der Sender (Sendetakt). Auf der Empfängerseite, wo die Daten wieder in paralleler Form weiterverarbeitet werden sollen, ist eine **seriell-parallel Wandlung** nötig:

Bei der Parallel-Seriell-Umwandlung werden die einzelnen Zeichenbits mit Hilfe eines Zeittakts auf die Leitung gegeben. Der Zeittakt bestimmt die **Übertragungsgeschwindigkeit** der einzelnen Bits. Man drückt diese Geschwindigkeit in **Bit/s** (**bps**, bits per second) aus. Übliche Übertragungsraten liegen heutzutage im Bereich zwischen 9600 Bit/s bis einige hundert Millionen Bit/s.

Die serielle Datenübertragung wird immer dann angewendet, wenn das Übertragungsmedium begrenzt ist, oder einen Kostenfaktor darstellt. Die serielle Datenübertragung bietet eine geringere Übertragungskapazität als die parallele Datenübertragung. Die Fortschritte in der Halbleitertechnik führten aber zu sehr schnellen kostengünstigen Seriell-Parallel-Wandlern, so dass die parallele Datenübertragung in vielen Bereichen verdrängt wurde.

## Vorteile der seriellen Datenübertragung gegenüber der parallelen Datenübertragung:

- Geringere Kosten da weniger Übertragungsleitungen,

- Größere Reichweite,

- Kein Übersprechen auf benachbarte Leitungen und kein Zeitversatz (*clock skew*).

#### Nachteil:

• Geringere Übertragungskapazität als bei paralleler Verarbeitung.

Bei der seriellen Übertragung muss der Zeitpunkt, zu dem die ankommenden Daten vom Empfänger übernommen werden sollen, präzise definiert sein. Der Empfänger muss wissen zu welchem Zeitpunkt er abtasten soll. Die Signalerkennung muss also gleichlaufend zur Signalerzeugung erfolgen.

Man unterscheidet zwischen synchroner und asynchroner serieller Übertragung.

## Das synchrone Verfahren

Beim synchronen Verfahren besteht ein festes Zeitraster, in dem die Binärzeichen eingebettet sind. Sender und Empfänger arbeiten mit dem gleichen Schritttakt und stehen ab Beginn des ersten Zeichens in einer festen Beziehung zueinander.

Die Synchronisation erfolgt am Anfang eines Datenblocks und bleibt während der gesamten Übertragung eines Blocks erhalten (Blocksynchronisation). Die Taktinformation kann auf einem separaten Kanal bereit gestellt werden (3 Leitungen) oder aber aus selbst taktenden Leitungscodes (Codes welche Nutzinformation und Taktinformation enthalten) abgeleitet werden. Die Blöcke selbst können asynchron versendet werden.

Die Übertragungsgeschwindigkeit ist eventuell veränderbar und kann dem Kanal angepasst werden. Das synchrone Verfahren verlangt, dass die Daten vor der Übertragung bereits vollständig vorhanden sind. Sie müssen also vor dem Versenden in einem Puffer zwischengespeichert werden.

## Das asynchrone Verfahren

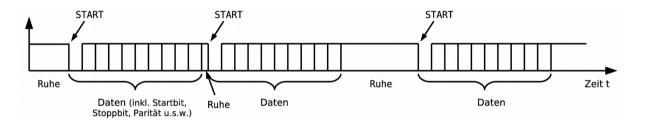

Bei der asynchronen Datenübertragung kann die Informationsübertragung zeichenweise zu einem beliebigen Zeitpunkt erfolgen.

Ein an einem PC arbeitender Benutzer sendet z. B. diese Zeichen in zufälligen unvorhersehbaren Intervallen. Sender (Tastatur) und Empfänger (PC) sind daher nur während der Übermittlung eines einzelnen Zeichens synchronisiert. Die Synchronisation ist durch eine festgelegte Bitrate, ein festgelegtes Datenformat sowie die Verwendung von Start- und Stoppbits möglich (keine Taktleitung).

Die asynchronen Übertragung beginnt mit einem Startbit und endet mit einem oder mehreren Stoppbits. Zusätzlich zum Zeichen können noch Kontrollbits (z. B. Parität) eingefügt werden.

## Das asynchrone und synchrone Verfahren im Vergleich

#### **Asynchrones Verfahren:**

Das Übertragen eines jeden Zeichens mit einem Start- und Stoppbit ist eine einfache, aber robuste und wirkungsvolle Synchronisationsmethode. Sie erfordert weder eine Pufferung der Zeichen, noch einen ständigen Gleichlauf zwischen Sender und Empfänger. Der Aufwand für Hardware ist gering, daher sind Datenendgeräte, die mit diesem Verfahren arbeiten, kostengünstig.

## **Synchrones Verfahren:**

Das synchrone Verfahren ist gegenüber der asynchronen Übertragung effektiver, weil innerhalb eines Datenblocks nur reine Daten (ohne Steuerbits) übertragen werden. Es wird immer dann eingesetzt, wenn es auf optimale Ausnutzung der Übertragungszeit ankommt.

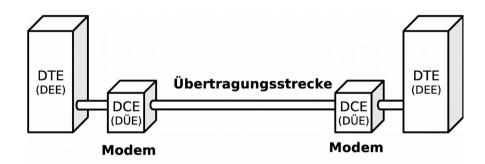

## Größere Entfernungen

Um digitale Signale über größere Entfernungen zu übertragen (z.B. Telefonleitung), benötigt man **Modem**s (**Mod**ulator-**Dem**odulator) an der Sendeseite und an der Empfangsseite. Das Modem realisiert durch eine Modulation die Umsetzung in Signale, die an den Übertragungsweg angepasst sind. Durch zusätzliche Datencodierung kann die Übertragung auch effizienter gemacht werden, da

pro Übertragungsschritt mehrere Bits gleichzeitig ausgesendet werden. Auf der Empfangsseite muss ebenfalls ein Modem für die Rückgewinnung der ausgesendeten Daten sorgen (Demodulation und Decodierung).

Folgende Bezeichnungen werden verwendet (deutsche Bezeichnungen in Klammern):

#### DTE: Data Terminal Equipment

ein Gerät, welches am Ende einer Übertragungsleitung angeschlossen ist, z. B. Computer, Terminal, Drucker oder Datalogger.

(DEE steht für Daten-End-Einrichtung)

#### DCE: Data Communication Equipment

Bezeichnet das Zusatzgerät, welches für die Fernübertragung benötigt wird, das Modem. (DÜE steht für **Daten-Übertragungs-Einrichtung**).

## **EIA-232**

Die **EIA-232**-Schnittstelle ist seit fast 50 Jahren standardisiert. Die Norm wurde mehrmals überarbeitet. Die aktuelle amerikanische Version der Norm heißt offiziell ANSI/EIA/TIA-232-F-1997 und ist aus dem Jahr 1997. Ebenso häufig wie die aktuelle Bezeichnung EIA-232 (EIA für *Electronic Industries Alliance*) findet man die alte Bezeichnung **RS-232** (RS für *Radio Sector* bzw. *Recommended Standard*) oder die Bezeichnung **V24**. Diese rührt von Empfehlungen des früheren CCITT (*Comité consultatif international télégraphique et téléphonique*), heute **ITU** (*International Telecommunication Union*) die für die Norm verwendet wurden (CCITT V.28 für elektrische Eigenschaften, CCITT V.24 für Protokoll"-Eigenschaften).

EIA-232 definiert an sich die Verbindung zwischen einem Terminal (DTE) und einem Modem (DCE), was Timing, Spannungspegel, Protokoll und Stecker betrifft.

Mikrocontroller bedienen sich oft der EIA-232-Schnittstelle, um mit externen Geräten in Kontakt zu treten. Auch wenn diese Schnittstelle schon viele Jahre besteht, reicht ihre Geschwindigkeit für übliche Anwendungen oft aus. Sie ist äußerst robust und erlaubt auch größere Kabellängen. USB-EIA-232-Wandler ermöglichen die Verbindung mit dem PC, falls keine serielle EIA-232-Schnittstelle mehr verfügbar ist.

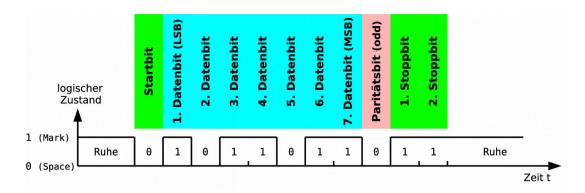

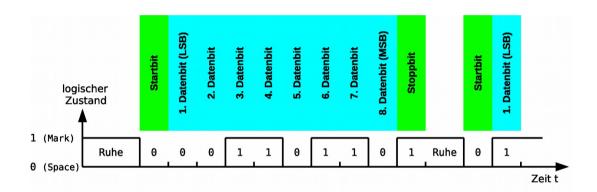

## Der Zeichenrahmen (SDU, Serial Data Unit)

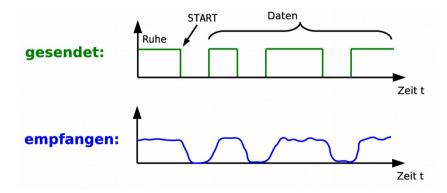

Jedes einzelne Zeichen wird innerhalb eines Zeichenrahmens (*frame*, **SDU**, *Serial Data Unit*) zwischen Steuerbits eingefasst. Im inaktiven Zustand (Ruhezustand, es wird kein Zeichen übertragen) wird die Übertragungsleitung auf logisch 1 (*Mark*) gehalten.

Der Beginn der Datenübertragung und damit auch die Synchronisation erfolgt mit Hilfe eines **Startbits** (logisch 0, **Space**), das an den Anfang eines jeden Zeichens gesetzt wird.

Anschließend werden die Datenbits ausgesendet. Je nach gewähltem Code können dies 5, 6, 7 oder 8 Bits sein. Am häufigsten ist die Übertragung mit 8 Bit.

Man beachte, dass das niederwertigste Datenbit (LSB, Least Significant Bit, D0) zuerst übertragen wird!

Nach den Daten wird ein **Paritätsbit** und ein, anderthalb oder zwei **Stoppbits** (logisch 1) übertragen.

Das Paritätsbit ist ein Kontrollbit, dient der Fehlererkennung, und bezieht sich nur auf die Datenbits. Der Vorteil dieses sehr einfachen aber wenig effektiven Schutzes gegen Übertragungsfehler ist, dass er durch die Hardware ausgeführt wird (im Baustein integriert) und somit keine Rechenzeit in Anspruch nimmt. Man unterscheidet:

• **gerade Parität:** (E, **even** parity) Das Paritätsbit wird so gesetzt, dass

die Summe der Einsen aus Datenbits und Paritätsbit

gerade ist.

• ungerade Parität: (O, odd parity) Das Paritätsbit wird so gesetzt, dass die

Summe der Einsen aus Datenbits und Paritätsbit

ungerade ist.

• **keine Parität:** (N, *no* parity) Die Parität wird nicht berücksichtigt

Das Paritätsbit nimmt den Wert an, der erforderlich ist, um die gewählte Parität für die Anzahl aller Eins-Werte zu erhalten.

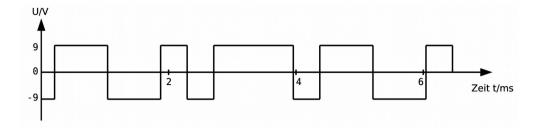

Die nächsten beiden Bilder zeigen jeweils ein Beispiel für die logischen Zustände der Datenleitung bei der Übertragung eines Zeichenrahmens.

**Beispiel 1:** 7 Datenbit (0b1101101 = 'm'), Ungerade Parität, 2 Stoppbit,

Kurzschreibweise: 702

**Beispiel 2:** 8 Datenbit (0b01101100 = 'l'), Ohne Parität, 1 Stoppbit

Kurzschreibweise: 8N1

Das nachfolgende Datenbyte wird zu einem beliebigen Zeitpunkt verschickt.

Die Übertragungsgeschwindigkeit der EIA-232 Schnittstelle liegt zwischen 300 bit/s und 115200 bit/s.

Bei jeder Signaländerung wird nur ein Bit übertragen. Die Übertragungsgeschwindigkeit ist somit der Baudrate (Signaländerung/Sekunde) bei EIA-232 gleichzusetzen<sup>4</sup>.

Heute werden durchweg höhere Bitraten als früher eingesetzt. Häufige Bitraten sind 2400, 4800, 9600, 14400, 19200, 28800, 38400, 57600 und 115200 bit/s (bzw. Baud (Bd)). Höhere Bitraten verringern die maximale Kabellänge (siehe: Die Reichweite von EIA-232)!

Empfänger und Sender müssen auf die gleiche Geschwindigkeit (Bit- bzw. Baudrate) und das gleiche Datenformat eingestellt werden (unter Datenformat versteht man die Zahl der Datenbits und Stoppbits sowie die Parität, Bsp.: 8N1).

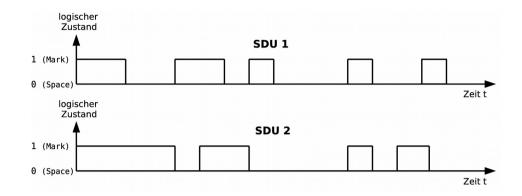

△ **C200** Bestimme aus den beiden folgenden Zeitaufnahmen einer Übertragung das mögliche Datenformat, die Anzahl der Sendeschritte (Bits) sowie das übermittelte ASCII-Zeichen, wenn mit 7 Datenbit gearbeitet wurde. Sind mehrere Möglichkeiten vorhanden, so gib sie alle an.

<sup>4</sup> Achtung! Bei fast allen anderen Schnittstellen gilt dies nicht, da dort meist mehrere Bits pro Signaländerung übertragen werden.

#### △ **C201**

- a) Zeichne einen Zeichenrahmen für die Übertragung eines 'Z' (8 Datenbit, ASCII-Code: 90(10)) mit gerader Parität und 2 Stoppbit.

- b) Berechne die Zeichenrate (Zeichengeschwindigkeit in Zeichen/s), wenn die Übertragungsgeschwindigkeit 115200 bit/s beträgt.

- c) Wie lange braucht ein Zeichen um übertragen zu werden?

- d) Wie lange braucht eine Textdatei um übertragen zu werden, wenn sie 64 kByte an Daten enthält?

## Die EIA-232-Schnittstellensignale

## Die wichtigsten Schnittstellensignale:

| 25 | 9 | Signal   | nal Beschreibung Beschreibung                     |                            | Art         | Richt.<br>PC M. | Null-<br>aktiv |

|----|---|----------|---------------------------------------------------|----------------------------|-------------|-----------------|----------------|

| 2  | 3 | TxD (SD) | Transmitter Data                                  | Sendedaten                 | Datenleit.  | <b>→</b>        |                |

| 3  | 2 | RxD      | Receiver Data                                     | Empfangsdaten              | Datenleit.  | <b>←</b>        |                |

| 4  | 7 | RTS      | Request to Send                                   | Sendeteil<br>eingeschaltet | Steuerleit. | <b>→</b>        | ja             |

| 5  | 8 | CTS (CS) | Clear to Send                                     | Sendebereitschaft          | Meldeleit.  | <b>←</b>        | ja             |

| 6  | 6 | DSR      | Data Set Ready                                    | Betriebsbereitschaft       | Meldeleit.  | <b>←</b>        | ja             |

| 7  | 5 | GND      | (Signal) Ground                                   | Betriebserde               | Erdleitung  |                 |                |

| 8  | 1 | DCD (CD) | Data Carrier Detect<br>(Data Channel<br>Received) | Empfangssignalpegel        | Meldeleit.  | <b>←</b>        | ja             |

| 20 | 4 | DTR (TR) | Data Terminal<br>Ready                            | Endgerät bereit            | Steuerleit. | <b>→</b>        | ja             |

| 22 | 9 | RI       | Ring Indicator                                    | Ankommender Ruf            | Meldeleit.  | <b>←</b>        | ja             |

#### 2 Datenleitungen

- 1 Masseleitung

- 2 Steuerleitungen

- 4 Meldeleitungen

Die Richtungsangabe gilt für eine Verbindung PC - Modem. Nullaktiv bezieht sich auf die Anschlüsse am Schnittstellenbaustein bzw. Port des Mikrocontroller (TTL-Pegel<sup>5</sup>). Die Melde- und Steuerleitungen werden also durch Ziehen des Anschlusses auf Nullpegel (*Low*, 0V) eingeschaltet.

Man erkennt, dass alle Signale aus der Sicht des steuernden Gerätes (PC, DTE) bezeichnet wurden. Da PC und Modem (DCE) bei bidirektionaler Betriebsweise senden und empfangen können, kann die Bezeichnung manchmal zur Verwirrung führen. Besonders, da die Bezeichnungen am Modem denen des PC entsprechen (Verbindung 1:1). Verbindet man allerdings zwei PCs miteinander so müssen die Leitungen gekreuzt werden (siehe Null-Modem-Verbindung).

Die allerwichtigsten Schnittstellensignale sind die beiden Datenleitungen "**Transmitter Data**" (**TxD**) und "**Receiver Data**" (**RxD**) sowie die Masseleitung (GND). Mit diesen drei Leitungen ist eine bidirektionale Datenübertragung möglich (unidirektional bereits mit zwei Leitungen).

EIA-232 wurde erschaffen um mit einem schnellen Terminal Daten an ein ein langsames Modem zu senden. Da das Modem oft die Daten nicht ausreichend schnell entgegennehmen konnte war eine Steuerung des Datenflusses nötig. Eine softwaremäßige Datenflusssteuerung hätte die Datenübertragung verlangsamt, so dass die Steuerung hardwaremäßig mit 2 Steuer – und 4 Meldeleitungen vorgenommen wurden.

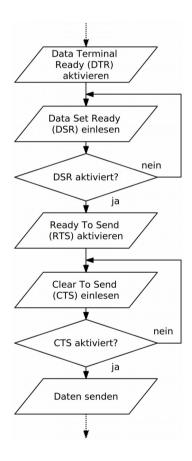

Die Steuerleitung "*Data Terminal Ready*" (**DTR**) und die Meldeleitung "*Data Set Ready*" (**DSR**) dienen dazu zu signalisieren, dass das jeweilige Gerät (*Data Terminal* ≡ PC; *Data Set* ≡ Modem) eingeschaltet ist. Die Leitungen sind während der gesamten Übertragung aktiviert. Bei modernen Geräten werden die Leitungen manchmal, entgegen ihrer ursprünglichen Bestimmung, für eine erweiterte Datenflusskontrolle eingesetzt.

Die eigentliche hardwaremäßige Flusskontrolle geschieht mittels der Steuerleitung "*Request To Send*" (RTS; "darf ich Senden?") mit der, der PC beim Modem anfragt, ob es bereit ist. Eine Aktivierung der Meldeleitung "*Clear To Send*" (CTS; "bin bereit!") leitet dann das Senden ein. Kann das Modem die eingehenden Daten nicht schnell genug verarbeiten, so deaktiviert es CTS. Der PC wartet dann so lange, bis CTS wieder aktiviert wird. In umgekehrter Richtung ist so eine Steuerung nicht vorgesehen (schnelles Modem, langsamer PC).

"*Data Carrier Detect*" (DCD, Träger auf der Telefonleitung vorhanden) und "*Ring Indicator*" (RI, ankommender Anruf) werden nur bei der Übertragung PC - Modem (DTE-DCE) benötigt. Sie werden heute oft nicht mehr verwendet!

Die serielle Schnittstelle wird sehr vielfältig bei sehr unterschiedlichen Geräten eingesetzt. Die Steuer und Meldeleitungen werden dabei öfter zweckentfremdet.

Bevor man zwei Geräte verbindet sollte man sich genaustes Informieren wie die Schnittstelle eingesetzt wird.

<sup>5</sup> Die Transistor-Transistor-Logik (TTL) ist eine Schaltungstechnik und bezeichnet eine Schaltkreisfamilie bei der bipolare Transistoren zur Realisierung von logischen Gattern verwendet wurden. Die TTL-Schaltkreisfamilie arbeitet mit einer Betriebsspannung von 5 Volt (±5 %). High-Pegel am Eingang ist dabei eine Spannung > 2 V (meist 5 V). Low-Pegel eine Spannung < 0,8 V (meist 0 V).

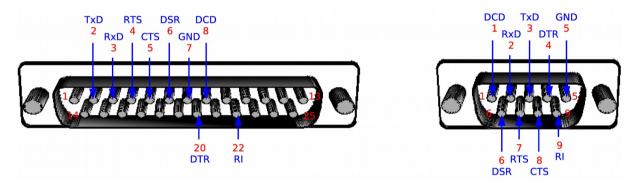

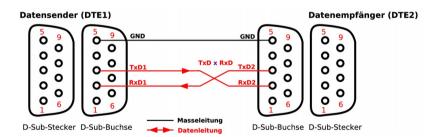

## **Die EIA-232-Verbindungen**

Für die EIA-232-Schnittstelle werden 9- oder 25-polige D-Sub-Buchsen oder Stecker (Das D steht wegen der Ähnlichkeit der Buchse mit dem Großbuchstaben D) verwendet, wobei die 25-polige Ausführung immer weniger eingesetzt wird.

Es gibt viele verschiedene Anschlussmöglichkeiten der Leitungen, um die einzelnen seriellen Geräten miteinander zu Verbinden. Welche Verbindungsmöglichkeit genutzt wird, hängt vom Geräte und der benötigten Übertragungssicherheit ab.

Meist wird beim PC ein 9-poliger **Stecker** (männlich, Stifte) benutzt. Am Modem wird eine Aufnahme-**Buchse** (weiblich, auch meist 9-polig) verwendet. Bei DTE-DCE-Verbindungskabel benötigt man also eine Buchse für den PC und einen Stecker für das Modem.

## **Steckerbelegung Draufsicht (männlich):**

Ändert man die Perspektive (Lötperspektive anstatt Draufsicht) so ändert auch die Nummerierung! Das gleiche gilt, wenn man eine Buchse statt einem Stecker in der gleichen Ansicht betrachtet.

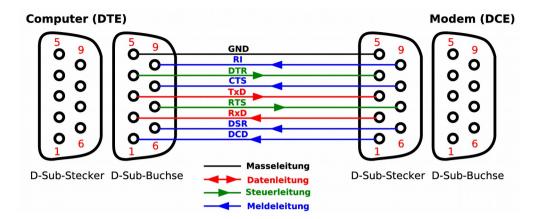

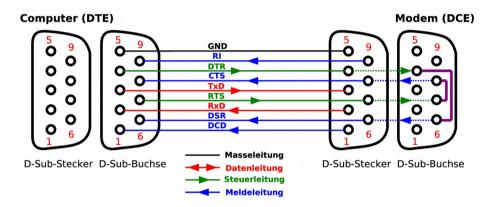

## Verbindung PC (DTE) - Modem (DCE)

Wie oben beschrieben erfolgt hier die Verbindungen 1:1. Ein solches Kabel hat auf DTE-Seite eine Buchse und auf DCE-Seite einen Stecker. Es sind alle Leitungen verbunden. Es werden allerdings auch Kabel verkauft, wo aus Kostengründen nicht alle Leitungen vorhanden sind.

Im Zweifelsfall soll man das Kabel immer durchmessen.

Die hardwaremäßige Datenflusskontrolle (Handshake) für die serielle Schnittstelle kann am PC einbzw. ausgeschaltet werden. Auch wenn ein Gerät keine hardwaremäßige Datenflusskontrolle benötigt, sollte man damit rechnen, dass am PC die hardwaremäßige Datenflusskontrolle eingeschaltet ist. Mit Brücken zwischen RTS und CTS bzw. DSR und DTR kann man den PC überlisten. Sein eigenes Steuersignal gaukelt ihm eine positive Antwort auf der Meldeleitung vor.

## Die Verbindung PC (DTE) – PC (DTE) (Nullmodemkabel)

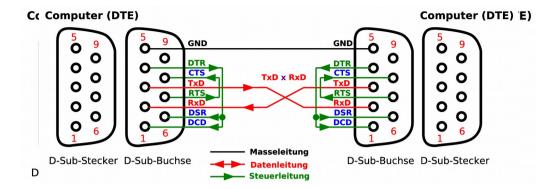

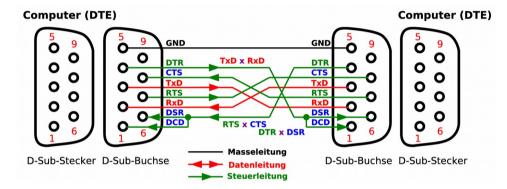

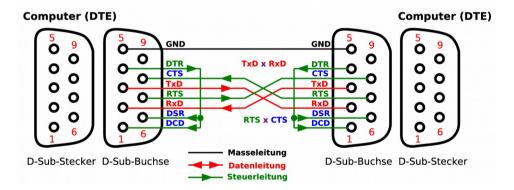

Es ist heute üblich auch zwei steuernde Geräte, zum Beispiel zwei PCs, miteinander zu verbinden. In diesem Fall ist die Sendeleitung des einen Gerätes die Empfangsleitung des anderen Gerätes und umgekehrt. Die Leitungen sind also zu kreuzen.

Dies gilt auch für die Steuer und Meldeleitungen, denn jeder Computer muss seinem Gegenüber ein Modem vortäuschen. Die Flusskontrolle funktioniert in beide Richtungen.

Kabel mit intern gekreuzten Leitungen nennt man **Null-Modem-Kabel**. Sie enthalten meist an beiden Enden Buchsen und sollten speziell gekennzeichnet werden um sie von anderen Kabeln unterscheiden zu können.

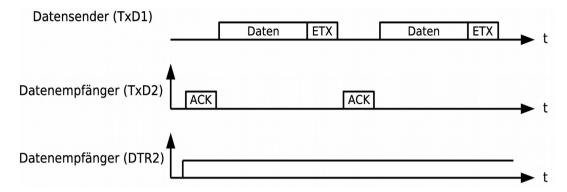

Für eine minimale Verbindung mit reinem Software-Handshake reicht die Datenleitungen zu kreuzen und somit drei Leitungen zu verwenden:

Um Probleme zu vermeiden, wenn eines der Geräte doch Meldeleitungen abfragt, kann die gebrückte Version verwendet werden:

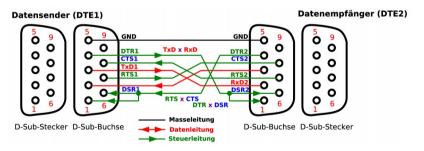

Für ein vollständiges Hardware-Protokoll müssen die Datenleitungen und vier Steuerleitungen gekreuzt werden. Hierbei kann dann, falls erwünscht, auch noch DCD mitversorgt werden. Die Meldeleitung RI entfällt, da ja kein Modem versorgt wird.

Um die Dicke des Kabels zu verringern oder wenn kein vollständiges Handshake implementiert ist, kann die abgespeckte Versionen verwendet werden.

Es existieren auch Null-Modem-Adapter die man auf 1:1-Kabel aufstecken kann, um ein Null-Modem-Kabel zu simulieren. Besonders praktisch sind Adapter die es erlauben mit Steckbrücken die Signalleitungen beliebig zu verdrahten. *Gender-Changer* ermöglichen zusätzlich den Wechsel von Buchse zu Stecker und umgekehrt. Andere Adapter ermöglichen auch die Änderung der Polzahl der Verbindungsstecker bzw. Buchsen.

Mit einer so genannten *Loopback*-Buchse kann man die Schnittstelle testen. Mit Brücken (TxD-RxD, RTS-CLS, DTR-DSR) werden alle Signale eines Gerätes direkt zum Empfangsteil des gleichen Gerätes zurückgeführt.

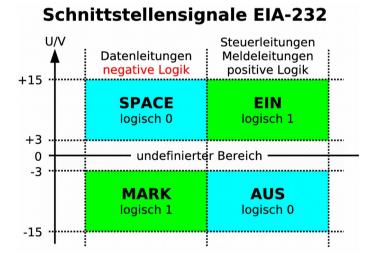

## Die Pegel der EIA-232-Schnittstellensignale

EIA-232 ist eine Schnittstelle, bei der die Information mittels Spannungspegel übertragen wird. (Spannungsschnittstelle im Gegensatz zu einer Stromschnittstelle wie z. B. MIDI).

Es wird bei der EIA-232-Schnittstelle keine Leistungsanpassung verwendet, da dabei die Spannungsverluste zu hoch wären. Die Leitung wird also nicht, wie bei vielen anderen schnelleren Schnittstellen üblich, mit einem Wellenwiderstand abgeschlossen. Dadurch treten aber Reflexionen auf der Leitung auf, die neben der Dämpfung der Leitung die Reichweite verringern.

Um akzeptable Reichweiten zu erhalten, muss die Spannungsdifferenz höher als bei TTL ausfallen. Der Pegel am Empfänger liegt zwischen +15 V und -15 V. Spannungen geringer als +3 V bzw. -3 V gelten als undefiniert. Umso höher die Spannungsdifferenz, umso größer die Reichweite. Sender müssen mindestens  $\pm 5$  V an einer Last von 3 bis 7 k $\Omega$  liefern. PCs arbeiten üblicherweise mit  $\pm 12$  V, Notebooks mit  $\pm 7$  bis 8 V.

Die Datenleitungen arbeiten mit negativer Logik, die Steuer und Meldeleitungen mit positiver Logik! Alle Leitungen des Schnittstellenbausteins bzw. des Ausgabeports des Controllers werden also invertiert!

Aus der negativen Logik der (nullaktiven) Steuer- und Meldeleitungen wird eine positive Logik. High-Pegel auf der Datenleitungen werden durch eine negative Spannung dargestellt.

Da 0 V als Spannungspegel nicht möglich ist, kann eine Unterbrechung der Leitung immer sofort erkannt werden.

△ **C202** Bestimme beim folgenden von einem Oszilloskopschirm abgezeichneten Bild das verwendete Datenformat (8 Datenbit), die Anzahl der Sendeschritte (Bits), das übermittelte ASCII-Zeichen sowie die Übertragungsrate.

## **Die Reichweite von EIA-232**

Mit Standardkabeln ist bei einer Baudrate von 19200 Baud eine Reichweite von um die 15 m möglich<sup>6</sup>. Mit Kabeln, welche eine besonders niedriger Kapazität aufweisen (z. B. nicht geschirmtes Netzwerkkabel UTP CAT-5), lassen auch 45 m erreichen. Folgende Tabelle zeigt Erfahrungswerte der Firma Texas Instruments (Quelle: wikipedia):

| Baudrate | max. Länge |

|----------|------------|

| 2.400    | 900 m      |

| 4.800    | 300 m      |

| 9.600    | 152 m      |

| 19.200   | 15 m       |

| 57.600   | 5 m        |

| 115.200  | <2 m       |

## Der Pegelwandlerbaustein 232

Eine digitale Schaltung mit TTL-Pegeln darf nicht ohne Pegelwandler an die serielle Schnittstelle angeschlossen werden, da sie sonst zerstört wird!

Will man mit TTL-Bausteinen die serielle Schnittstelle benutzen, so muss eine TTL/EIA-232-Pegelanpassung vorgenommen werden. Die Halbleiterindustrie bietet solche Pegelwandler als integrierte Schaltkreise an. Sie werden als "232"-ICs bezeichnet. Je nach Hersteller sind verschiedene Buchstaben voran gesetzt.

Diese Bausteine benötigen als Spannungsversorgung meist nur eine positive Spannung von 5 V. Mit zwei externen Kondensatoren wird die Spannung verdoppelt. Zwei weitere externen Kondensatoren helfen die Spannung zu invertieren. Inverter in der Sende- und in der Empfangsstufe sorgen für die Umwandlung der positiven in die negative Logik und umgekehrt. Im Anhang ist die Beschaltung eines solchen ICs zu sehen.

<sup>6</sup> Die Lastkapazität, die hauptsächlich durch die Kabelkapazität bestimmt wird, soll laut Norm 2500 pF nicht überschreiten.

## Die Datenflusskontrolle (bei EIA-232)

Bei der asynchronen Datenübertragung wird eine Datenflusssteuerung oder Datenflusskontrolle (*data flow control*) benötigt, wenn die Gefahr besteht, dass der Sender Daten zu schnell zum Empfänger sendet, so dass eine kontinuierliche Datenübermittlung ohne Verluste nicht möglich ist.

Der langsamere Empfänger muss also die Möglichkeit erhalten die Datenübertragung zeitweise zu unterbrechen, da er sonst mit Daten überlastet wird, und diese dadurch verloren gehen könnten.

Die Steuerung dieser Unterbrechungen ist Aufgabe der Datenflusskontrolle. Es gibt hierzu zwei Möglichkeiten:

- **Software-Handshake** mit im Datenstrom eingebauten Steuerinformationen.

- *Hardware-Handshake* mit zusätzlichen Leitungen (Steuer- und Meldeleitungen).

## **Die Software-Flusskontrolle**

Bei der Software-Flusskontrolle (*Software-Handshake*, Software-Protokoll) geschieht die Kontrolle (Steuerung) mit im seriellen Datenstrom eingebetteten Steuerzeichen. Zwei bekannte Formen des Software-Handshake sind das

- XON/XOFF-Protokoll und das

- ETX/ACK-Protokoll.

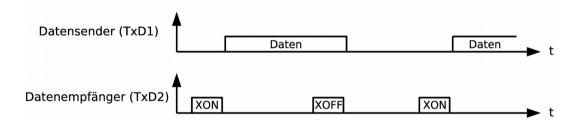

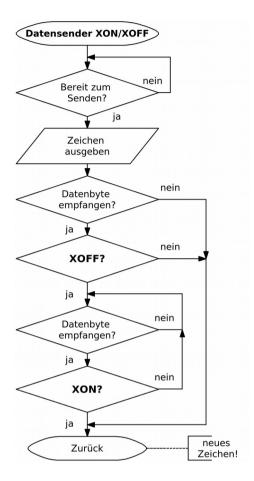

### Das XON/XOFF-Protokoll

Zur Kontrolle werden die beiden Steuerzeichen **XON** (Transmission ON) und **XOFF** (Transmission OFF) verwendet. Die Codierung der Steuerzeichen **XON** und **XOFF** kann unterschiedlich sein, meistens wird für **XON** das ASCII-Steuerzeichen "**DC1**" (11h) und für **XOFF** das ASCII-Steuerzeichen "**DC3**" (13h) verwendet.

Der Empfänger bestimmt die Flusskontrolle. Er sendet bei Empfangsbereitschaft einen **XON**-Zeichen an den Sender. Sobald der Sender dieses Steuerzeichen erkannt hat, beginnt er mit dem Senden von Daten. Kann der Empfänger keine weiteren Daten mehr aufzunehmen, weil zum Beispiel sein Datenpuffer voll ist, so gibt er dem Sender mit einem **XOFF**-Zeichen zu verstehen, dass dieser die Datensendung aussetzen soll. Der Sender arbeitet erst nach dem Empfang eines erneuten **XON**-Zeichens weiter.

Für das **X0N/X0FF** - Protokoll werden nur drei Leitungen benötigt (2 gekreuzte Datenleitungen und Betriebserde). Da gleichzeitig Daten übertragen werden können, handelt es sich um eine Vollduplex-Verbindung.

### Mögliches Flussdiagramm für ein Unterprogramm zum Senden:

## Das ETX/ACK-Protokoll

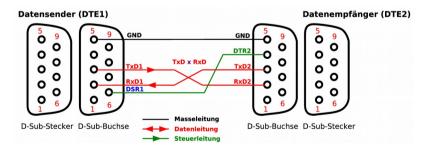

Beim **ETX/ACK**-Protokoll wird eine **zusätzliche Steuerleitung** (**DTR** (Empfänger) nach **DSR**) eingesetzt. Es ist also kein reines Software-Protokoll.

Es werden **Datenpakete** übertragen, wobei die Länge der Pakete von der Pufferkapazität des Empfängers abhängt (oft 128 Byte). Jedes Paket schließt mit dem ASCII-Steuerzeichen **ETX** (03h, *End of Text*) ab. Die Paketlänge muss so bestimmt sein, dass es zu keinem Überlauf des Empfangspuffers kommt! Die Betriebsbereitschaft des Empfängers wird mit der Steuerleitung **DTR** signalisiert (High-Pegel). Anschließend sendet der Empfänger das ASCII-Steuerzeichen **ACK** (06h, *Acknowledge*). Der Sender übermittelt daraufhin das Datenpaket, das mit dem **ETX** abgeschlossen ist. Ist der Empfangspuffer nach dem Empfang der Daten noch nicht voll und zur weiteren Aufnahme von Daten bereit, sendet der Empfänger erneut ein **ACK** an den Sender. Der Sender kann nun das nächste Datenpaket übermitteln.

Es handelt sich hierbei um eine Halbduplex-Verbindung, da abwechselnd Daten übertragen werden.

#### Nachteile der Software-Flusskontrolle:

Die Software-Flusskontrolle ist durch die benötigten Steuerzeichen weniger effektiv als die Hardware-Flusskontrolle. Auch können durch die Steuerzeichen nicht alle 256 Zeichen eines Byte genutzt werden, was die Übertragung binärer Daten erschwert, da diese umcodiert werden müssen. Die Software-Flusskontrolle sollte nur genutzt werden, wenn es keine Alternative gibt.

## Die Hardware-Flusskontrolle

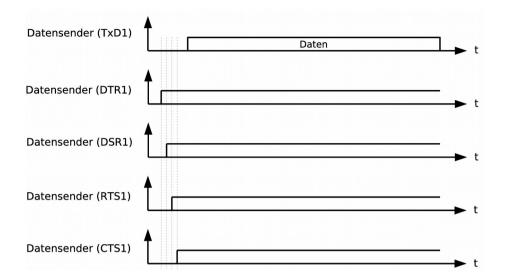

Die Funktionsweise der Hardware-Flusskontrolle (*Hardware-Handshake*, Hardware-Protokoll) bei der asynchronen seriellen Schnittstelle wurde schon beim Kennenlernen der Steuerleitungen besprochen (PC-Modem). Im Folgenden soll nochmal das Handshake beim Aufbau einer Verbindung zwischen zwei Daten-End-Einrichtungen (PC oder Mikrocontroller) vom sendenden PC (Controller) aus mit Hilfe eines Zeitdiagramms und eines Flussdiagramms betrachtet werden.

Bemerkung: Die EIA-232-Schnittstelle sowie ihr Hardware-Handshake wurde konzipiert und genormt für eine Datenverbindung PC-Modem. Heute wird sie oft zur Realisierung von Datenverbindung ohne Verwendung eines Modems eingesetzt. Viele Gerätehersteller haben aus Kostengründen aber nur Fragmente der Schnittstelle implementiert. Die Verbindung mit Hardware-Protokoll zwischen unterschiedlichen so genannten kompatiblen Geräten ist daher oft schwierig und zeitraubend.

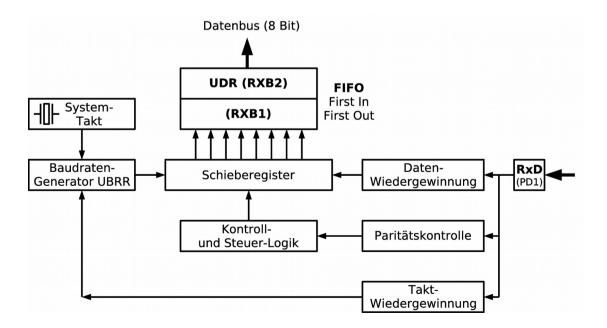

## Der USART des ATmega32A

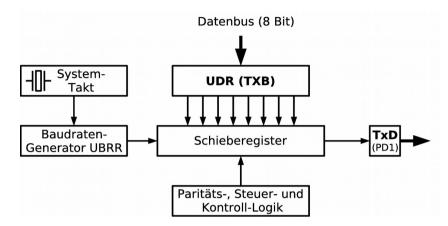

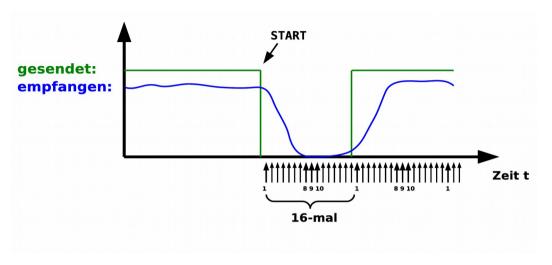

Viele Mikrocontroller besitzen eine so genannte **UART** (*Universal Asynchronous Receiver/ Transmitter*), also einen universelle Sender- und Empfänger-Baustein, der **asynchron** Daten übertragen kann. Seine Aufgabe ist es beim Senden mit Hilfe eines Schieberegisters einen seriellen digitalen Datenstrom mit einem fixen Rahmen aufzubauen. Beim Empfang muss eine Synchronisation über Start- und Stopp-Bit und eine bekannte Bitrate erfolgen, da kein Taktsignal vorhanden ist. Dazu wird das empfangene Signal mit einer mehrfachen Taktfrequenz abgetastet (siehe später).

Der ATmega32A besitzt, genau wie der ATmega8A und ATmega16A einen **USART** (*Universal Synchronous/Asynchronous Receiver/ Transmitter*), welche zusätzlich zu den Eigenschaften des UART auch noch synchron übertragen kann<sup>7</sup>.

Die USART des ATmega32A hat getrennte Sende- und Empfangspuffer und ermöglicht so einen Vollduplexbetrieb. Er kann drei verschiedene Interrupts auslösen, so dass eine effektive Datenübertragung mit Interruptsteuerung möglich ist. Rahmen-, Paritäts- und Überlauffehler werden erkannt.

Weitere hier nicht genutzte Eigenschaften sind die Multiprozessor-Datenübertragung oder das Arbeiten mit doppelter Übertragungsgeschwindigkeit.

**Bemerkung:** Eine EIA-232-Schnittstelle kann mit niedriger Bitrate und entsprechendem Aufwand natürlich auch ohne UART bzw. USART softwaremäßig realisiert werden.

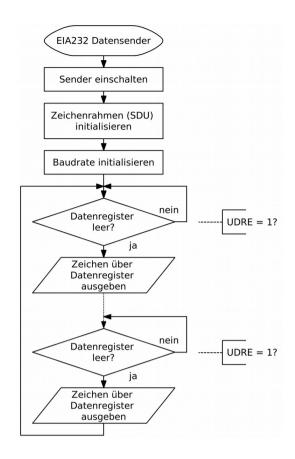

## <u>Die Initialisierung der USART</u>

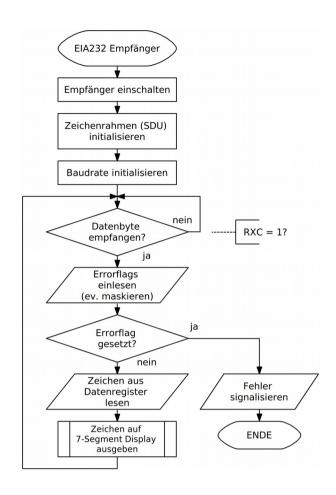

Damit eine Kommunikation über eine serielle Schnittstelle möglich wird, müssen folgende Parameter bei Sender und Empfänger richtig initialisiert werden:

- **1.** Parameter welche die Schnittstelle betreffen (Sender/Empfänger einschalten, asynchron/synchron, Polling oder Interrupt)

- 2. Das Datenformat.

- **3.** Die Baudrate.

Bevor diese Parameter umgestellt werden sollte im Zweifelsfall geklärt werden ob alle vorigen Kommunikationen abgeschlossen sind (TXC- und RXC-Flags überprüfen!).

Zur Initialisierung und Statusabfrage des USART dienen die drei Register:

• UCSRA, UCSRB und UCSRC (USART Control and Status Register A, B, C).

Die **Baudrate** wird über das Doppelregister:

UBRR (USART Baud Rate Register) eingestellt.

Es besteht aus UBRRH, und UBRRL.

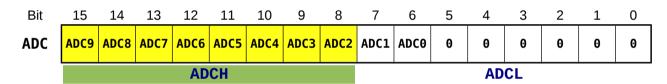

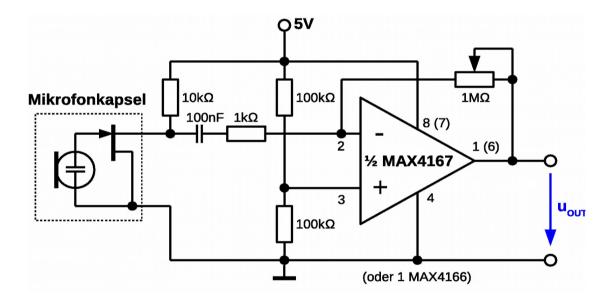

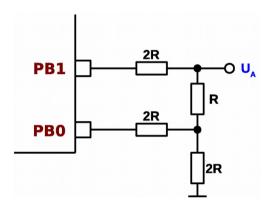

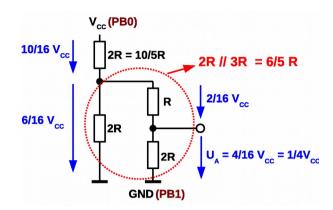

<sup>7</sup> Es wird dann zusätzlich zu den Datenleitungen auch noch eine Taktleitung benötigt.